ESD & Latch-up Testing

Home » Services » Microelectronics Test & Engineering » ESD & Latch-up Testing

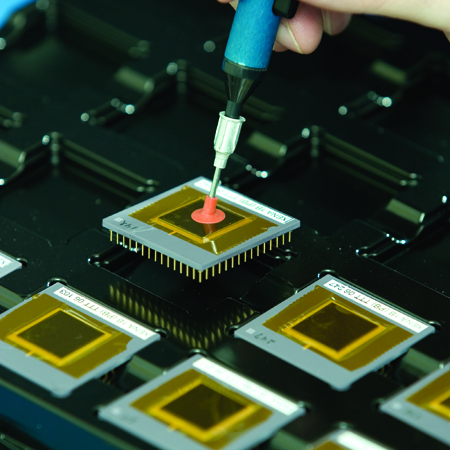

EAG Laboratories is an industry leader in ESD testing (Electrostatic Discharge) and latch-up testing. Our highly experienced engineering team uses their industry leading knowledge and years of real world experience with the latest semiconductor technologies, circuit design, and device physics to optimize our customer’s ESD and latch-up results. When you choose EAG, you will be working together with recognized experts in the field of ESD testing and latch-up testing. We are committed to providing our customers with the most up-to-date testing methodologies, along with technical interpretation of the test data and accurate assessment of the results. Additionally, EAG’s ITAR-compliant testing laboratory ensures protection for our aerospace and defense clients.

Our in-house PCB team can also create custom ESD fixtures quickly to help speed your time to results. In addition, EAG’s ESD team is part of a much larger service organization that provides customers ready access to world-class failure analysis, environmental/reliability testing, FIB circuit edit, electron microscopy and ATE test services.

With six Thermo Fisher Scientific Orion CDM machines available, EAG Laboratories has the most capacity and latest equipment for charged device model testing. Our ISO 9001:2015-certified full-service laboratories also offer failure analysis, advanced microscopy and materials testing to determine root cause of ESD failures.

HBM, MM and CDM Testing

Applicable HBM Specs

- JEDEC: JS-001-2017 and JESD22-A114 (superseded by JS-001-2017)

- Department of Defense: MIL-STD-883, Method 3015.7

- Automotive Electronics Council: AEC-Q100-002 and AEC-Q101-001 (based on JS-001-2017)

- ESD Association: ESD STM 5.1-1998 (superseded by JS-001-2017)

Applicable CDM Specs

- JEDEC: JS-002-2018 and JESD22-C101 (superseded by JS-002-2018)

- Automotive Electronics Council: AEC-Q100-011 and AEC-Q101-005 (based on JS-002-2018)

- ESD Association: ESDA STM 5.3.1-1999 (superseded by JS-002-2018)

Applicable MM Specs

- JEDEC: JESD22-A115 (obsoleted by JEDEC, but still available)

- Automotive Electronics Council: AEC-Q100-003 and AEC-Q101-002 (obsoleted by AEC, but still available)

- ESD Association: ESD STM 5.2-1999 (obsoleted by ESDA, but still available)

Latch Up Testing

Although latch-up testing is performed on the same automated testers as ESD testing, the tests are dramatically different. ESD testing is not done under bias. Latch-up testing is performed with the DUT powered, and signals are applied to the part to place it in a stable, low current configuration. A specialized ESD/LU worksheet is used to set up automated testers, such as the Thermo Scientific Mk2 or Mk4. Each tester channel has the unique ability to be programmed as a power supply, signal pin, or vectored pin.

The goal in IC latch-up testing is to trigger and monitor a potential latch-up event, where the stress pulse activates a parasitic transistor structure within a CMOS or Bi-CMOS process technology. Latch-up testing is fundamentally about the chip’s physical layout, how circuit blocks are situated relative to one another, and how unanticipated charge is removed from physical elements in the semiconductor material.

Latch-up testing is done according to the current revision of the JEDEC latch-up specification, but testing can also be done according to the previous revisions of JESD78. Testing can be done at a customer specified ambient temperature, from 25°C to 125°C. Because there are so many variables, latch-up testing is quoted on a case by case basis, based on the statement of work, estimated engineering time to create a working test, machine time to execute the test, and customer requested reporting.

Applicable LU Specs

- JEDEC: JESD78E

- Automotive Electronics Council: AEC-Q100-004 (based on JESD78E)

Transmission Line Pulse (TLP) Testing

Transmission Line Pulse testing, or TLP testing, is a method for semiconductor characterization of Electrostatic Discharge (ESD) protection structures. In the Transmission Line Pulse test, high current pulses are applied to the pin under test (PUT) at successively higher levels through a coaxial cable of specified length. The applied pulses are of a current amplitude and duration representative of the Human Body Model (HBM) ESD/LU worksheet request event (or a Charged Device Model – CDM – event in the case of Very Fast TLP, or VF-TLP). The incident and reflected pulses are evaluated, and a voltage-current (V-I) curve is developed that describes the response of an ESD protection structure to the applied TLP stresses. The Transmission Line Pulse test is unique because the current pulses can be on the order of Amps, and the TLP test results can show the turn-on, snap-back, and hold characteristics of the ESD protection structure.

Related Resources

Transmission Line Pulse testing is useful in two very important ways. First of all, TLP may be used to characterize Input/Output (I/O) pad cells on test chips for new process technologies and Intellectual Property (IP). TLP is very useful in developing simulation parameters, and for making qualitative comparisons of the relative merit of different ESD protection schemes for innovative pad cell designs. Secondly, TLP may be used as an electrical failure analysis tool, often in combination with conventional, standards-based component ESD testing.

TLP testing is done according to the ESDA TLP test method, ESDA SP5.5-2003. TLP is quoted on a case by case basis, based on the scope of the work requested; estimated engineering time to perform the test, and customer requested reporting.

Applicable TLP Specs

- ESDA SP5.5-2003 (ESD Association)

Would you like to learn more about ESD & Latch-up Testing?

Contact us today for your ESD & Latch-up Testing needs. Please complete the form below to have an EAG expert contact you.